В плисине использую только два банка выводов из четырёх. Незадействованные банки решил не запитывать.

Вопрос, что делать с питанием этих бавнков, оставить болтаться в воздухе, или посадить на землю?

Вопрос, что делать с питанием этих бавнков, оставить болтаться в воздухе, или посадить на землю?

>Вопрос, что делать с питанием этих бавнков, оставить болтаться в воздухе, или посадить на землю?

Ответ: прочитать соотвествующий аппноут от производителя. Например, Hardware Design Guide Consideration.

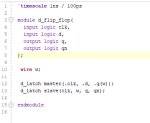

Как на SystemVerilog реализуются такие схемы? По идее на HDL они должны реализовываться очень легко, но я не представляю, как это сделать. На входе должен быть многочлен степени n (видимо, тип данных logic [3:0]), на выходе многочлен степени n + 3. Там, где отводы вниз, это операция xor. Как это сделать?

always @(posedge clk) begin

z1 <= input;

z2 <= z1;

z3 <= z2;

end

assign output = input + z1 + z3;

Можно и параметризовать. Со сдвиговым регистром проблем не должно быть, потом поразрядное и с полиномом, апосле унарный КСОР (т.е. все разряды регистра ксорятся друг с другом).

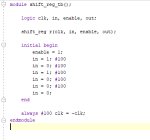

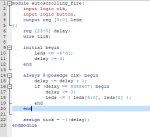

А у меня правильно сделано?

module shift_reg(input logic clk,

input logic in,

input logic enable,

output logic out);

reg [2:0] data;

always @(posedge clk) begin

if (enable)

data <= { data[1:0], in };

end

assign out = data[2];

endmodule

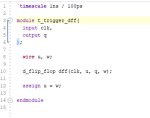

Как правильно написать тестбенч к этой штуке? У меня сигнал clk при такой реализаици имеет неизвестное значение, не меняется.

Зачем нужна последняя строчка?

Да, она лишняя, точно.

А как можно все коэффициенты получившегося полинома вывести на шину? Например, известно, что максимальная степень полинома будет 6, тогда можно сделать шину out logic [5:0] выходной и на нее записывать коэффициенты полинома. Как это делать в этой схеме?

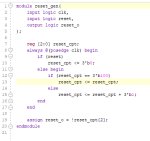

Как в тестбенче задавать изменения клока?

Вот тут, например

Вот тут, например

module modulename #(parameter B = 6-1)(...output logic [B:0],...);

Смысл? У тебя тестбенч скорее всего функциональный, будет работать на любой частоте клока, хоть там период в фемтосекунду поставь.

Назначь ему валидное значение в начале. И заодно используй forever, чтобы было яснее, что этот код не описывает железо и не предназначен для синтеза.

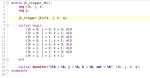

initial begin

clk = 1;

forever #5 clk =!clk;

end

Что будет если плисину с коммерческим рэнжем температур (от 0 до 70) выставить на небольшой мороз (до -10С). Сильно всё по пизде пойдёт даже если допустим делать все клоки с двойным+ запасом?

Как задаются индексы шины при конкатенации шин? Вот например:

wire [1:0] dataIn;

assign dataIn = {d1,d0};

Тут dataIn[0] содержит сигнал d0 или d1? Или это не имеет значения?

wire [1:0] dataIn;

assign dataIn = {d1,d0};

Тут dataIn[0] содержит сигнал d0 или d1? Или это не имеет значения?

Дубина, если нужен расширенный температурный диапазон, то надо было покупать соответствующую ревизию.

Что будет? Параметры в даташите указаны при определённых температурах. Как минимум генерация поплывёт.

>генерация поплывёт.

Какая ещё генерация? Ты про тактовый сигнал? Но почти во всех полисах нет встроенного тактового генератора как в микроконтроллерах (когда только кварцевый резонатор снаружи). А есть всего лишь максимум синтезируемые кольцевые генераторы на инверторах, которые почти никто не использует.

>Дубина, если нужен расширенный температурный диапазон, то надо было покупать соответствующую ревизию.

Зумеры не слышали про дефицит. Ты lead time на диджикее видел?

>Что будет

С вероятностью 95+% - ничего критичного. Народ вон копеечные ардуины на аэростатах в стратосферу запускает, и ничего, работают.

У ардуины в спеках температуры от –40°C до +125°C. По меркам FPGA это уже military grade, ваенные технологии.

Если единичный экземпляр проверь натурно.

Если серия ставь подогрев.

То что справа то младшее, что слева старшее.

Нет, у атмег -40...+85С, это индастриал.

Милитари - это -60...+125 или шире.

В даташите у атмеги 328p все зарактеристики даются от -40 до 125, т.е. это не просто absolute maximum rating.

Если нетрудно укажи где конкретно смотреть, или ещё лучше запости скриншот. Всё что я смог нагуглить, уже не помню где, это только фразу что

>банки должны быть подключены к какому-то питанию.

У меня в китайском нищеплисе явно написано

> The device requires all the I/O's VCCIO to be connected to the power supply.

Плюс для некоторых банок есть ограничение, что питание не должно быть меньше какого-то, потому что от него работает какая-то дополнительная хуйня внутри чипа и она привязана к этой банке.

Прямо сейчас у нас вообще два банка к питанию не подключены, подключены только их земли к земле, плюсовые выводы болтаются в воздухе и при этом всё работает. Но меня точит червь сомнения что это не правильною В следующей ревизии платы я плюсовые выводы подключил на землю впослед через конденсатор. Вот теперь думаю насколько это адекватно...

> Прямо сейчас у нас вообще два банка к питанию не подключены

Вам что, жалко дорожку к паду подвести? Или вы пытаетесь впихнуть какой-нибудь BGA780 в двухслойную плату?

>Или вы пытаетесь впихнуть какой-нибудь BGA780 в двухслойную плату?

Ну почти, + вторичный источник питания главный конструктор нагружать не хочет, а он тот ещё чудило.

По верилогу вот есть

https://www.youtube.com/playlist?list=PL4UMfOeGYsvblwrP3VYKHq11xgkxVqoUj

По виваде хз.

Vivado на линуксах работает?

Почему не устанавливается из aur?

==> Сборка пакета vivado 2022.2-1 (Ср 15 фев 2023 15:23:44)

==> Проверка зависимостей для запуска...

==> Проверка зависимостей для сборки...

==> Получение исходных файлов...

-> Загрузка Xilinx_Unified_2022.2_1014_8888.tar.gz...

curl: (37) Couldn't open file /Xilinx_Unified_2022.2_1014_8888.tar.gz

==> ОШИБКА: Ошибка при загрузке 'file:///Xilinx_Unified_2022.2_1014_8888.tar.gz'

Прерывание...

-> ошибка сборки: vivado

>Since the download of the installer is locked behind a login wall, it needs to be downloaded manually as outlined above and placed in the same directory as the PKGBUILD.

Ты эту часть прочитал/сделал? (Тебе на самом деле даже не нужен AUR и школоарч как таковой, инсталлятор с сайта Хилых встанет на любые прыщи, но только в обход менеджера пакетов.)

плис в россии мертв

>плис в россии мертв

Дядя Вова сказал в говне-моченым, чтобы сделали красиво!!

Мне из России доступ с загрузкам на сайте xilinx запрещен, даже через тор браузер не дает скачать. Получается в России остается только качать вивадо с торрентов?

Берёшь любой прокси/VPN (плюс фейкомыло), создаёшь фейковый аккаунт какого-нибудь греческого студента Хохлоса Пидороса, чтобы получить URL для скачивания. А потом качаешь каким-нибудь wget непосредственно с https://xilinx-ax-dl.entitlenow.com/ уже напрямую.

У тутошнего анона уровень всё же повыше, потому спрошу тут.

Пристало как-то к моим липким ручонкам советские процессоры

КР1801ВМ1

КР1801ВМ2

КР1810ВМ86

КР580ВМ80А

КР580ИК80А

КР1820ВЕ1А

КР1814ВЕ5

Хотел бы я использовать их в своих ёбаподелках, но им для работы нужны внешние микросхемы оперативной памяти и ПЗУ для хранения программы, да ещё порты ввода-вывода. А их то, как раз, у меня и нет.

Что-то можно подобрать из современной элементной базы для их замены?

Пристало как-то к моим липким ручонкам советские процессоры

КР1801ВМ1

КР1801ВМ2

КР1810ВМ86

КР580ВМ80А

КР580ИК80А

КР1820ВЕ1А

КР1814ВЕ5

Хотел бы я использовать их в своих ёбаподелках, но им для работы нужны внешние микросхемы оперативной памяти и ПЗУ для хранения программы, да ещё порты ввода-вывода. А их то, как раз, у меня и нет.

Что-то можно подобрать из современной элементной базы для их замены?

Дяденька, ты в какой жопе мира обитаешь?

Загляни на тот же Авито со словами 580ВВ51А, 580ВВ55А, 580ВИ53, 580ВН59, 580ГФ24, 580ВК28/38 - рублей по 40 и меньше можно выловить каждую микросхему (новую и не паянную).

По памяти - вообще любая подойдет, хоть на 55(50), что 70 нс - хотя лучше кешпамять на 10-15 нс искать. Главное - напряжение питания 5В должно быть. Для ПЗУ - ищи 28 серию ПЗУ (мало и почти на ходу перешивать можно) или 29F серию - только блоками стирать, записывать можно и по кусочкам. Требования те же - 5В питание.

Что бы не ебаться с кучей рассыпчатой логики - ищи ПЛИС типа EPM7128S (остерегайся подделок/залоченных).

Если прям вообще ничего нет - ищи преобразователи уровней, ПЛИС - будешь использовать в двухпортовом режиме память плис для имитации ОЗУ/ПЗУ/отладки, как и имитировать параллельные порты ввода-вывода.

PS Выбрось каку КР580ИК80А. Это тоже самое что и КР580ВМ80А.

>КР580ВМ80А

>КР580ИК80А

Три питания +5, -5, +13. Как делать будешь? Далее, как написал анон выше, мало подрубить память, нужно ещё о прерываниям подумать, о таймерах, uart, собственно сами порты параллельные вв55. Дофига всего. А чего ради? Чтобы получить сильно ухудшенное подобие атмеги? Таким образом если и делать такое, то просто так, для развлечения. Но и то лучше взять вм85, будет намного меньше всего и с питанием проще. Сам вот прям сейчас понемногу паяю на макетке поделку на 8085. Просто так, без каких-либо задач.

>КР1814ВЕ5

Это с масочным ПЗУ, оно похоже никак не может выполнять код из внешнего. Можешь выкинуть.

>КР1810ВМ86

В целом во многом аналогично вм80. И если я не ошибаюсь, то намного проще на 8088 делать из-за восьмибитной шины, можно такую же восьмиразпядную память использовать, если я не ошибаюсь. С учётом цены всего этого проще тебе взять К1810ВМ86.

>КР1801ВМ1

>КР1801ВМ2

Эти интересные конечно, тем что система команд от pdp-11. Но тоже такое себе.

>КР1820ВЕ1А

Вот с этими вероятно проще всего, вроде как им только ПЗУ снаружи требуется. Но в них очень мало всего.

И анон выше прав, самое простое это подрубить к плисине. Только некоторая ассиметрия получится, особенно в варианте с fpga с памятью внутри, ведь в такую плисину влезет процессор посущественнее этого раритета.

>проще тебе взять К1810ВМ86.

ВМ88, опечатка

>анон выше прав, самое простое это подрубить к плисине.

Я тут подумал ещё немного и похоже с современной элементной базой оптимально будет подключать эти древние процессоры к атмегам или ещё каким микроконтроллерам, так будет не только проще, но и дешевле одной только параллельной EEPROM.

Звучит хорошо. Собрался использовать мега128 или 256 для эмуляции (если хранить все адресное пространство ПЗУ+ОЗУ во флеше) или мегу послабее если собрался эмулировать например 8килобайт ОЗУ? Убедил.

Как ОЗУ собрался на меге эмулировать? Есть всего килобайт-два ОЗУ в лучшем случае которые будут немного засраны работающей программой эмуляции.

Надо понимать что ОЗУ и ПЗУ - память с произвольным доступом. Как собрался на частоте около 2 МГц быстренько находить что надо и выдавать на шину? Тут конвейеризация или предвыборка не всегда спасет или поможет.

Ну да, у нас для 8080 есть шагатель на триггере с помощью которого можно хоть руками переключателями каждый байт на шине выставлять-читать. Оно надо такое счастье?

Как же хардкор под названием ROM эмулятор на ОЗУ для отладки и выполнения программы на полной скорости процессора?

Параллельный ввод-вывод можно сделать на триггерах(регистрах) - их наверняка в любой жопе мира можно найти и к ним понадобится немного рассыпчатой логики для декодера адресов.

Последовательный ввод-вывод.. Отображать регистр UDR и остальные для юарта меги в адресное пространство процессора? Хитер..

Прерывания? А оно надо на начальном этапе?

Как-то не особо возбуждает. Даже не поФАПаешь на такие извращения. https://habr.com/ru/post/446048/

>Как собрался на частоте около 2 МГц быстренько находить что надо и выдавать на шину?

Учти что команды у атмеги выполняются быстрее чем у 8080. Надо такты посчитать, может и на такой частоте будет. Ну и можно микроконтроллер посущественнее взять, если так сильно нужно будет.

>Как-то не особо возбуждает. Даже не поФАПаешь на такие извращения.

Вот именно, поэтому "современная" элементная база тут несколько неуместна.

> А чего ради?

Ради DAT FEEL чего только не городят: http://www.s100computers.com/My System Index Page.htm

> Только некоторая ассиметрия получится, особенно в варианте с fpga с памятью внутри, ведь в такую плисину влезет процессор посущественнее этого раритета.

Так ПЛИСины разные бывают, не обязательно туда седьмой Кинтекс пихать:https://www.mattmillman.com/projects/8od/

Очень давно не писал под AVR.. Давай прикинем условный код:

.org int1_vector

rjmp rom_emul - вход в прерывание 4 такта + прыжок 2 такта

...

.org 280h

rom_emul: in zh,pinA - 1 такт

in zl, pinB - 1 такт

lpm r16,z -3 такта

out portC,r16 - 1 такт

reti - 4 такта

=4+2+1+1+3+1+4= 16 тактов.

Вот и соснул. При 16 МГц тактовой максимум 1МГц (1миллисекунда) в идеальных условиях можно получить (если снаружи повесить логику декодера адресов, RD на отдельный вход прерывания повесить на мелких мегах. на толстых мегах порты уже как ОЗУ и их через in/out не потыкаешь, только через lds/sts которые 2 такта требуют).

Хорошо хоть не бзданул "вручную тактируй". У 8080 есть минимальная частота ниже которой он начнет люто глючить, поэтому менее 500 КГц (кварц 9*500=4.5МГц) ему лучше не подавать, а тормозить шагателем.

> Ну и можно микроконтроллер посущественнее взять, если так сильно нужно будет.

На том же Хабре была статья как кто-то пытался эмулировать в биосе на иса шине жесткий диск. У иса шины тактовая около 8 МГц и все что могло пойти не так - пошло не так..

Так что сильно проще немного порвать пердак и найти реальные микросхемки, а не ебаться с эмуляторами особенно когда хер знает как оно работает и особенности поведения которые в даташите не видны.

Я вот никак 580ВВ79(8279) не запущу кодом с обломков компа. Какую-то херню выдает на индикаторы.

>особенно когда хер знает как оно работает

Что именно? ОЗУ и ПЗУ ну и вв55? Анон же не собрался втыкать весь комплект кр580, а вероятно только память и параллельный порт.

>когда хер знает как оно работает и особенности поведения которые в даташите не видны.

Временные диаграммы чтения и записи для 8080 есть, а что тебе ещё нужно чтобы их запустить?

>Хорошо хоть не бзданул "вручную тактируй".

Тоже мне откровения. Также можно задействовать сигнал ready, оно специально для медленной фигни на шине.

>Что именно? ОЗУ и ПЗУ ну и вв55?

Попроще ничего не нашел? Например 580ВТ42 и срать что не периферия... Мультиплексор и счетчик внутри. Чего не взял ВТ57, ВГ75, ВВ51, ВИ53 как пример?

Даже сам Интел в руководстве как-то писал - нужен параллельный порт? Берем 589ИР12 (8212) и радуемся жизни. Вот тут точно никаких вопросов нет как он работает.

>Временные диаграммы чтения и записи для 8080 есть, а что тебе ещё нужно чтобы их запустить?

Подключить - да, достаточно. Программировать - нет, недостаточно. В какой регистр что писать? Какие есть запрещенные комбинации которые ломают логику работы? Вот с ходу вопрос - что будет при чтении регистра состояния ВВ55? Такие мелочи надо знать прежде чем писать эмулятор.

http://www.nedopc.org/forum/viewtopic.php?f=91&t=17383

>Тоже мне откровения. Также можно задействовать сигнал ready, оно специально для медленной фигни на шине.

Nice. Немного не в тему, но новые версии старых процессоров/микроконтроллеров иногда имеют приписку "fully static operation" и их реально можно вручную тактировать и смотреть как оно работает в замедленном виде.

Куда делся анон с процессорами? Может прояснит ситуацию что у него есть и что доступно.

>Берем 589ИР12

Ну можно и так.

>писать эмулятор.

Вообще то анон с процессорами не упоминал эмуляторы, а лишь бы запустить. Как раз наоборот, упоминал современную элементную базу. Поэтому вероятно не важно все это.

Анон с профессорами итт.

Отвечу всем и сразу.

Всякие ПДП и уарты не нужны. Достаточно портов в/в. Их отображать в адресное пространство. Для реализации дешифрации адреса, по теории, даже рассыпухи не нужно, можно использовать старший разряд шины адреса.

Под современной элементной базой имел ввиду микросхемы ОЗУ, ПЗУ совместимые с этими процессорами, но выпускаемые промышленностью на данный момент, это чтобы с поиском советских не ипаться, также важен прайс, он должен быть ниже современных микроконтроллеров, иначе овчинка выделки не стоит.

Если советские ещё можно достать на авите, то, с одной стороны, это хорошо, с другой, никаких гарантий нет, что они рабочие, или, что не кинут.

Эмуляцию на МК или плисине не рассматриваю, ибо экономически не выгодно, любая занюханная Мега по функционалу и стоимости далеко впереди, ну может не далеко, но всё же. Да и как сказано выше, зачем эмулировать обвес на МК/ПЛИС когда там уже есть процессор как минимум не хуже.

Эмуляцию ПЗУ на плисине тут имеет смысл рассматривать только в качестве возможности отладки ПО.

Кстати, под эти профессоры есть ассемблер, о сишном компиляторе я даже не мечтаю, а то в машинных кодах писать не очень хочется?

>Три питания +5, -5, +13. Как делать будешь?

Над этим пока не думал. Может удастся обойтись без минусового?

Отвечу всем и сразу.

Всякие ПДП и уарты не нужны. Достаточно портов в/в. Их отображать в адресное пространство. Для реализации дешифрации адреса, по теории, даже рассыпухи не нужно, можно использовать старший разряд шины адреса.

Под современной элементной базой имел ввиду микросхемы ОЗУ, ПЗУ совместимые с этими процессорами, но выпускаемые промышленностью на данный момент, это чтобы с поиском советских не ипаться, также важен прайс, он должен быть ниже современных микроконтроллеров, иначе овчинка выделки не стоит.

Если советские ещё можно достать на авите, то, с одной стороны, это хорошо, с другой, никаких гарантий нет, что они рабочие, или, что не кинут.

Эмуляцию на МК или плисине не рассматриваю, ибо экономически не выгодно, любая занюханная Мега по функционалу и стоимости далеко впереди, ну может не далеко, но всё же. Да и как сказано выше, зачем эмулировать обвес на МК/ПЛИС когда там уже есть процессор как минимум не хуже.

Эмуляцию ПЗУ на плисине тут имеет смысл рассматривать только в качестве возможности отладки ПО.

Кстати, под эти профессоры есть ассемблер, о сишном компиляторе я даже не мечтаю, а то в машинных кодах писать не очень хочется?

>Три питания +5, -5, +13. Как делать будешь?

Над этим пока не думал. Может удастся обойтись без минусового?

> Может удастся обойтись без минусового?

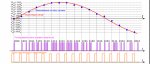

Минусовый можно получить из плюсового элементарным buck-конвертером. Выставить в нём резисторами 5В. Входной + подключить правильно, там где должно быть выходное напряжение подключить землю, а из земли брать заветные -5В. Buck-конвертер будет работать на виртуальной земле VGND выставляя её так, чтобы VGND + 5 = 0 (потому что выход подключён к земле). Т.е. на выходе и будут заветные -5В. Пикрил.

>Под современной элементной базой имел ввиду микросхемы ОЗУ, ПЗУ совместимые с этими процессорами, но выпускаемые промышленностью на данный момент

Взаимоисключающие параграфы. Микросхемы с питанием 5В уже давно не выпускают. Все флеши и память сейчас 3.3, 2.5, 1.8в...

Только "недавнее" старье искать. Что бы не ныл - например A29040B-70F, K6T1008C2E-DB55, AT29C040A (довольно интересная - можно кусками по 256 байт перешивать), DS1245Y-70+ (ОЗУ как ПЗУ если батарея живая).

>также важен прайс, он должен быть ниже современных микроконтроллеров, иначе овчинка выделки не стоит.

Ебаный эффективный менеджер? Какого хуя ты забыл? Повыебываться как наебал систему, давайте мне премию, я молодец? Пиздуй шариться по помойкам - там за бесплатно найдешь, время такого биомусора ничего не стоит.

До тебя мудака походу не доходит что "хобби" - здесь эта экономическая составляющая на хую вертится так как в большинстве случаев важен процесс/результат, а не наебалово системы в промышленных масштабах.

Если собрался на продажу делать - просто съеби из этого треда на другие доски и там ной что 5 центов за память - это дораха, мне надо бесплатно пару вагонов.

Зачем тебе это?

У устройств на таких камнях будут неадекватные габариты и стоимость.

Посмотри в сторону китайских МК, самые дешевые - аналоги stm32f030, risc-v (ch32v00x) и 8051, производителей можно посмотреть на lcsc. Оригинальный stm32f030f4p6 150 руб стоит.

Если дохуя импортозамещение, у ангстрема был контроллер, похожий на древний пик, наверняка он дешевый.

>также важен прайс, он должен быть ниже современных микроконтроллеров

>ибо экономически не выгодно

https://habr.com/ru/post/678330/

"Микроконтроллер PMS152-S08. Всё почти тоже самое, но с большим объёмом памяти программ (1,25 KW), 11 битным ШИМ контроллером SuperLED, двумя пинами внешних прерываний и на 2 ножки больше.

Стоимость: 0,088$ (от 150 штук 0,064$)."

Уважаемый менеджер, примите заказ:

CYRS1645KV18-250GCMB 144-Mbit QDR® II+ SRAM - нужно 20 шт

MT29F128G08AMCABH2-10ITZ:A (Micron NAND Flash SLC 128G 16GX8) - 32 шт

8A34041 (8-Channel Universal Frequency Translator) - 5шт

AD9213 (radio frequency (RF) analog-to-digital converter (ADC)) - 13 шт

ZU48DR-G1517 (Xilinx ZYNQ UltraScale+ RFSoC) - 10 шт

Для пробного заказа хватит. Цена надо понимать должна быть менее 8 центов за чип, если больше - сразу идите нахер.

Жду счет на оплату с ценами, условиями и сроками поставки.

>и 8051

Не триггери, а? Недавно открыл для себя STC.

Вот это постарались - никаких тебе внешних анальноогороженных погромматоров/отладчиков, достаточно 3.3/5V UART и Keil + ему поебать напряжение питания - и 3.3 и 5В хавает.

https://aliexpress.ru/item/1005004879211209.html

Цена реальная, 1$. Доставили. Его прям не запускал еще, а старую версию https://aliexpress.ru/item/1005005072706151.html запускал (делал через интерфейс внешней памяти загружалку ОЗУ для 580ВМ80А по компорту).

>также важен прайс, он должен быть ниже современных микроконтроллеров

Посмотри цены на параллельные ПЗУ. Хотя бы 28C64, 27C64 и подобные, анон выше ещё упоминал. Так вот даже распайка на алиэкспрессе сейчас рублей по 50 за штуку. А ещё нужно ОЗУ, регистр для порта и что-то для дешифрации адреса. Это помимо напряжения +12, а -5 можно и не подавать, как-то будет работать, только без гарантий.

Поэтому никак оно не будет дешевле современных микроконтроллеров.

>цены на параллельные ПЗУ.

И даже последовательные 24C08 и прочие самые дешёвые на lcsc по $0.06 за штуку, при том что микроконтроллеры там же есть по $0.08.

Ну никак не будет дешевле готового микроконтроллера.

>Кстати, под эти профессоры есть ассемблер

Для 8080 разумеется. Можно ещё от z80 использовать.

Зато

>КР1801ВМ1

>КР1801ВМ2

Это pdp-11, первая сишечка для них и делалась.

>27C64

Может... Нинада? Все столбы в округе погаснут в попытках достать ДРЛ лампу для стирания этой классики.

Почему все забыли про программатор параллельной ПЗУ? Чем код то зашивать для отладки или работы? Сколько программатор стоит? Как или из чего его собирать? Намечается огромная дырень в бюджете как минимум на панельки. Дораха!

Для особо упертых или упоротых - есть и не классика 27 серии с электрическим стиранием, а не ультрафиолетом - "The W27C020 is a high speed, low power Electrically Erasable and Programmable Read Only Memory organized as 262144x8 bits that operates on a single 5 volt power supply, The W27C020 provides an electrical chip erase function."

>микроконтроллеры там же есть по $0.08

О, щас я тебя обоссу. К этим копеечным мк, которые, кстати, чаще всего OTP, нужен свой программатор. Для отладки требуется дорогая дев. борда, симулирующая работу этих мк. С тулчейном там всё настолько грустно и плохо, что ты охуеешь. Я уж молчу про всратую документацию на чинглише и отсутствие ерраты.

В общем, для говорящих хомяков и т.п. в миллионных тиражах есть смысл поебаться и заморочиться с этими копеечными мк, а для себя, для хобби они совершенно непригодны.

>Почему все забыли про программатор параллельной ПЗУ?

Потому что настолько очевидно что он необходим, что и писать не нужно. Если программатора нет, то придется разориться, самое простое взять на алиэкспрессе xgecu t48, около 4000 рублей стоит всего лишь.

>ДРЛ лампу для стирания этой классики.

На авито бактерицидную лампу взять. По любому дешевле программатора будет.

>которые, кстати, чаще всего OTP

Если брать тот по ссылке выше на хабр (это не я притащил), то у них есть и перезаписываемые чуть дороже.

>Для отладки требуется дорогая дев. борда, симулирующая работу этих мк.

Отлаживайся на перезаписываемых.

>нужен свой программатор.

Для параллельной ПЗУ все равно нужен программатор.

>С тулчейном там всё настолько грустно и плохо, что ты охуеешь.

Для 8080 по сути только ассемблер будет, с ним и сравнивай.

>в миллионных тиражах есть смысл поебаться и заморочиться с этими копеечными мк, а для себя, для хобби они совершенно непригодны.

Опять же сравнивай с КР580.

Не нравится такое, можно сравнить с STM32G030F6P6 за $0.67. Где найдешь дешевле параллельное ПЗУ, ОЗУ, регистр и мелочевку для дешифрации адреса?

>Не нравится такое, можно сравнить с STM32G030F6P6 за $0.67. Где найдешь дешевле параллельное ПЗУ, ОЗУ, регистр и мелочевку для дешифрации адреса?

Не ебу, к некрофилии отношения не имею.

Я лишь указал, что МК за 8 центов - это бесполезный хлам.

Как же хорошо зашел троллинг про 8 центов.

>Я лишь указал, что МК за 8 центов - это бесполезный хлам.

Хлам не хлам... Надо ТЗ читать:

>Под современной элементной базой имел ввиду микросхемы ОЗУ, ПЗУ совместимые с этими процессорами, но выпускаемые промышленностью на данный момент, это чтобы с поиском советских не ипаться, также важен прайс, он должен быть ниже современных микроконтроллеров, иначе овчинка выделки не стоит.

>также важен прайс, он должен быть ниже современных микроконтроллеров

>прайс ... ниже современных микроконтроллеров

>прайс ... ниже

Так что пусть не выебывается и берет что есть (предложено) или ищет дешевле 8 центов. Вот и весь посыл. Ой, а про достав.очка он наверное совсем забыл.. Найти ОЗУ или ПЗУ за 8 центов и менее включая достав.очка? Самому интересно - получится у него или нет?

Ты где? Народ уже соскучился, нашел и предложил варианты, а ты молчишь..

Дай угадаю - увидев слово "погромматор" уже сразу слился, так как стоит он сильно больше чем самый задроченный современный МК?

>Я лишь указал, что МК за 8 центов - это бесполезный хлам.

Хлам не хлам... Надо ТЗ читать:

>Под современной элементной базой имел ввиду микросхемы ОЗУ, ПЗУ совместимые с этими процессорами, но выпускаемые промышленностью на данный момент, это чтобы с поиском советских не ипаться, также важен прайс, он должен быть ниже современных микроконтроллеров, иначе овчинка выделки не стоит.

>также важен прайс, он должен быть ниже современных микроконтроллеров

>прайс ... ниже современных микроконтроллеров

>прайс ... ниже

Так что пусть не выебывается и берет что есть (предложено) или ищет дешевле 8 центов. Вот и весь посыл. Ой, а про достав.очка он наверное совсем забыл.. Найти ОЗУ или ПЗУ за 8 центов и менее включая достав.очка? Самому интересно - получится у него или нет?

Ты где? Народ уже соскучился, нашел и предложил варианты, а ты молчишь..

Дай угадаю - увидев слово "погромматор" уже сразу слился, так как стоит он сильно больше чем самый задроченный современный МК?

>Не ебу, к некрофилии отношения не имею.

Хоть википедию открыл бы. Этого хватило бы чтобы понять что у них внутри нет ни ОЗУ, ни ПЗУ и нужно лепить снаружи параллельные. И с питанием что-то делать.

>Я лишь указал, что МК за 8 центов - это бесполезный хлам.

Это очевидно всем. Только по сравнению с минимальной системой на КР580 эти микроконтроллеры очень даже ничего. Так что твое высказывание не в тему тут.

>или ищет дешевле 8 центов.

Даже STM32 из тех что помельче, будут дешевле чем докупать всю обвязку к КР580ВМ80А.

Пошла подмена понятий?

>Даже STM32 из тех что помельче, будут дешевле чем докупать всю обвязку к КР580ВМ80А.

Как собрался используя STM32 запускать КР580ВМ80А? Схемку нацарапай.

ОЗУ и ПЗУ допустим через wait сделаешь как и порты ввода-вывода. Чем тактировать собрался КР580ВМ80А? Ему 12В по хорошему надо с крутыми фронтами и уже не получится используя выводы с 5volt tolerant качать 12В сигнал.

В system guide написано что сигналы RDY и RESET не просто так идут через системный тактовый генератор - нужна жесткая привязка для синхронизации ибо можно загнать старичка в маразматическое состояние.

>Как собрался используя STM32 запускать КР580ВМ80А?

Никак. Тут сравнивали цены на готовые микроконтроллеры с ценой на всю минимальную обвязку КР580ВМ80А. Я про это и написал.

И если тебе так неймётся, бери лучше ВМ85.

А обвязка тут при том что у анона сам ВМ80А уже есть и тратиться ему только на "обвязку". И хочет он чтобы было дешевле готового микроконтроллера. Это если ты не читал обсуждение сначала.

> Может... Нинада?

Надо Федя… Надо! (ей обычной бактерицидной лампы хватит https://mysku.club/blog/aliexpress/76928.html )

> О, щас я тебя обоссу. К этим копеечным мк, которые, кстати, чаще всего OTP, нужен свой программатор. Для отладки требуется дорогая дев. борда, симулирующая работу этих мк. С тулчейном там всё настолько грустно и плохо, что ты охуеешь.

Конкретно для STC8 отладочная плата стоит в районе десяти баксов (или даже дешевле, но это будет просто кусок тестолита, с припаяным STC8G1), программируется обычным преобразователем USB-UART, а SDCC вообще бесплатен (ну или взять Keil с ближайшего рутрекера). Вот документация, таки да — на редкость всратая.

> Для 8080 по сути только ассемблер будет

Ну, вроде, кто-то пытался SDCC допилить, чтобы можно было для 8080 использовать, не боясь попадания Z80-only кода в выхлоп компилятора.

Ему, всё-таки, проще просто фапать и не выёбывааться: https://github.com/dekuNukem/FAP80 С аутентичной обвязкой тех времён есть смысл связываться только если хочется вспомнить молодость и DAT FEEL времён УМК-80 и Корвет-06Ц.

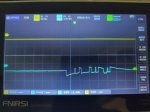

Моя заброшенная цацка.

Питание от 5В (вход снизу справа и там же виден преобразователь 5 в 12), -5 из микросхемки на 8 ног в нижнем левом углу.

Кварц где-то проебан из панельки. Снизу слева - вход для платки с stc8 которая подключает читает-пишет ОЗУ которое работает как ПЗУ.

MAX7128S в PLCC84 - клей для всего этого и декодер адресов.

Сверху типа системная шина для подключения периферии.

Грубые схемотехнические просчеты отправили ее на свалку и переделку.

Неужели это так сложно найти и собрать в нынешнее время то?

Питание от 5В (вход снизу справа и там же виден преобразователь 5 в 12), -5 из микросхемки на 8 ног в нижнем левом углу.

Кварц где-то проебан из панельки. Снизу слева - вход для платки с stc8 которая подключает читает-пишет ОЗУ которое работает как ПЗУ.

MAX7128S в PLCC84 - клей для всего этого и декодер адресов.

Сверху типа системная шина для подключения периферии.

Грубые схемотехнические просчеты отправили ее на свалку и переделку.

Неужели это так сложно найти и собрать в нынешнее время то?

> Неужели это так сложно найти и собрать в нынешнее время то?

Таки да. Потому как регулярно оказывается, что КР1810ГФ84 есть только в одном магазине, том самом где нет КР1810ВН59. И оба с физлицами не работают.

Кокая няша

А некоторые напрягли свою клоаку и собрали маленькую каллекцию которая далеко не в 8 центов обошлась... На бумажке написано ПЛИСАНАМ

ВМ85 в верхнем правом углу. 589ИК03 нет (есть, на работке осталась, по фотке с полным комплектом деанон будет).

Зачем старье типа ВМ80А?

Народ на 589 серии (интеловская 3000) собирал аппаратный эмулятор i8080 который гнался на 10 МГц что ли (те раз в 5 быстрее оригинала). Сиди, собирай процессор на 589 серии. У них полное описание дается - и схема и прошивки и как работает..

На фоне так и недособранный ЮТ-88 какой-то модификации на 580ВМ80А.

Кому интересно отвериложить все это? Да, уйти от физических микросхем и перенести их в ПЛИС как есть, вместе с двунаправленными выводами (знаю что их нет в ПЛИС) так что бы взял любую CPLD и зашил туда любую микросхемку (естественно если она влезет по объему))

>КР1810ГФ84

Так это для ВМ86.

А так у меня на работе много 8284, среди хлама который недовыкинули. И КР580 много разных.

>И оба с физлицами не работают.

У anion.ru есть КР1834ГФ84А, КМОП версия этого, если я правильно понял.

>вместе с двунаправленными выводами (знаю что их нет в ПЛИС)

Есть. Только на ногах, а не внутри. Так что если не очень много, то снаружи можно ноги соединить для такого.

>Ему, всё-таки, проще просто фапать и не выёбывааться: https://github.com/dekuNukem/FAP80 С аутентичной обвязкой тех времён есть смысл связываться только если хочется вспомнить

Нет. Упоминалась минимальная система, ОЗУ+ПЗУ и один порт ногами дрыгать. Ни таймеров ни прерываний не требуется. Так что хватит гф24, ла3, вв55 или регистр, ну и сами памяти. Не упростит в таком случае CPLD ничего.

А ещё проще вм85 взять, тогда отпадает питание и гф24, бонусом получается немного прерываний.

>Только на ногах, а не внутри.

То что на ногах есть - знаю, это не новость. А вот то что внутри нет - пичалька. Приходится всякие wishbone/avalon/axi/.../ шин изобретать что бы внутри эмулировать общую шину, а так хочется без всяких переходников/оберток/прочего соединять модули между собой как на реальной плате через те же 245 буферы.

https://github.com/1801BM1/vm80a/blob/master/org/rtl/vm80a.v

Очень тихо ФАПаю на это. На мой взгляд самая адекватная моделька где НЕ выкинули "бесполезные" выводы типа wait rdy hold hlda которых нет в "эмуляторе" Радио-86 РК и подобных. Клоака люто полыхает от этой модели - в няшечную FPGA EPF10K10 в PLCC84 не влезает, а в CPLD EPM1270 влетает со свистом.

Может есть отвериложенные модельки ВМ86 ВМ88 и подобных процессоров? Z80 не в счет - их клоакой хуй версий.

Хуйня какой-то этот ваш ПЛИС. Все настолько сложное, что интересный проект будешь делать годами, а всякие триггеры, АЛУ и мультиплексоры нет смысла реализовывать на кристалле и даже нельзя никому показать. Чисто умозрительное задротство.

Весь плис это душное сидение в моделсиме. Даже реализовать из рабочего ничего нельзя, все это - какие-то кубики, части одного целого, а все целое - проект на вечность времени. Веб-программирование и то интереснее, там хоть сразу получается что-то рабочее. Оправдывайтесь, говноеды.

Анон с профессорами итт.

>Ты где? Народ уже соскучился, нашел и предложил варианты, а ты молчишь..

Сорямба, сейчас нет возможности отвечать каждый день.

А я смотрю тема животрепещущая.

Ну ты чего подорвался на ровном месте?

Как уже говорил, хочу использовать их в своих ебаподелках, а они хоть и ёба, но всё же должны выполнять какую-то полезную функцию, а не быть самими для себя. Дроч ради дроча это не моё. Я понимаю, некоторые угарают по восстановлению ретро копуктеров, времяпрепровождение не хуже других, но это не мой случай. Может быть когда-нибудь потом.

В общем я понял, что со своими микросхемками я соснул. Технологии с тех пор шагнули слишком далеко, чтобы пытаться что-то делать на этом старье.

А погромматор у меня, кстати, есть, Тритон v5.3т. И лампа есть от стиралки.

>Это pdp-11, первая сишечка для них и делалась.

Где бы её ещё найти...

Не совсем понял, ну пока и не срочно, потом может повнимательнее посмотрю.

Что делает? Зачем плис?

> Приходится всякие wishbone/avalon/axi/.../ шин изобретать

Чёт ты махнул. Достаточно самого простого арбитра шины.

>Может есть отвериложенные модельки ВМ86 ВМ88 и подобных процессоров?

А в чём сложность? Была бы только исчерпывающая документация.

Ещё тут по сусекам поскрёб, кой чего интересного нашёл. Позже покажу.

>Ты где? Народ уже соскучился, нашел и предложил варианты, а ты молчишь..

Сорямба, сейчас нет возможности отвечать каждый день.

А я смотрю тема животрепещущая.

Ну ты чего подорвался на ровном месте?

Как уже говорил, хочу использовать их в своих ебаподелках, а они хоть и ёба, но всё же должны выполнять какую-то полезную функцию, а не быть самими для себя. Дроч ради дроча это не моё. Я понимаю, некоторые угарают по восстановлению ретро копуктеров, времяпрепровождение не хуже других, но это не мой случай. Может быть когда-нибудь потом.

В общем я понял, что со своими микросхемками я соснул. Технологии с тех пор шагнули слишком далеко, чтобы пытаться что-то делать на этом старье.

А погромматор у меня, кстати, есть, Тритон v5.3т. И лампа есть от стиралки.

>Это pdp-11, первая сишечка для них и делалась.

Где бы её ещё найти...

Не совсем понял, ну пока и не срочно, потом может повнимательнее посмотрю.

Что делает? Зачем плис?

> Приходится всякие wishbone/avalon/axi/.../ шин изобретать

Чёт ты махнул. Достаточно самого простого арбитра шины.

>Может есть отвериложенные модельки ВМ86 ВМ88 и подобных процессоров?

А в чём сложность? Была бы только исчерпывающая документация.

Ещё тут по сусекам поскрёб, кой чего интересного нашёл. Позже покажу.

Что ты будешь делать когда тебе потребуется обработать сигналов штук 100 у которых частоты под 50 МГц, м?

Сдрисни отсюда, вебмакака.

>потребуется обработать сигналов штук 100 у которых частоты под 50 МГц

Это какой usecase? Откуда сигналы? Какая логика их обработки?

Пусть будет стрёмная хуёвая ФАР.

В оборонке работаешь?

Какая логика применяется к таким сигналам? Преобразование Фурье?

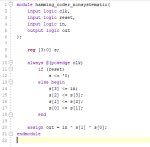

Почему при помощи этого делителя частоты не получается поморгать диодом? Диод не горит и загорается только при нажатии ресет.

Ты бы хоть строчки нумеровал.

>загорается только при нажатии ресет

Потому что при ресете твой cnt как раз равен нулю, и срабатывает условие в нижней строчке.

>Диод не горит

Потому что когда твой cnt инкриминируется по кругу, в нулевом состоянии он прибывает всего 1/10000000 от всего времени и ты тупо не видишь такие короткие подмигивания.

И чё тя не устраивает? Пишешь рандомизированный тестбенч, прогоняешь через него модуль, тест проходит успешно, получаешь свою порцию дофамина вместе с чувством превосходства над перекладывателями JSONов.

Если не нравится что предложил этот анон, могу предложить свое недавнее. Для видео из КМОП матрицы каждый кадр получать гистограмму, сделать гамма-коррекцию, усиление (умножение) со смещением (для вытягивания контраста), сделать линейный фильтр 5х5 и медианный 3х3 ну и ещё биннинг придется сделать. Автоматическая регулировка длительности экспозиции и установка значений для вытягивания контраста по полученной гистограмме уже в софт-процессоре.

Как будешь делать без ПЛИС? Можно конечно ДСП взять, но и с ними не так просто и я не умею их готовить

Ты ещё про дебайер забыл. Самая вычислительно сложная часть, если её по уму делать, с адаптивной интерполяцией по контурам изображения.

У меня монохромная матрица, мне проще. Цветные фигня для большинства задач, пишу как любитель звёзды фотографировать.

Из того что не написал, пришлось сделать ресайзинг. Делалось для замены камеры на другой матрице и нужно было со старыми объективами обеспечить прежние поля зрения. Я бы выбрал матрицу с другим размером пикселя чтобы так не извращаться, но начальник хотел заимствовать все из другого отдела, только прошивку немного скорректировать. Только не получилось, требовались слишком разные форматы на выходе. Да и схему пришлось переделать с импортозамещением всей мелочевки.

>usecase

Говори по-русски, прошмандовка ты пиндосовская.

100 Гбитый коммутатор. Как тебе такой юзкейс?

Виваду спиздил уже у кровавых пиндосов, патриот? Ты б лучше начал искоренение пиндосского влияния со своих 100гбитных коммутаторов. Ой, не можешь? ) А чё так? )))

>100 Гбитый коммутатор

Понятно. Но это все твоя работа, а не хобби. Получается что в качестве хобби на FPGA хуй что сделаешь.

Блядь, проектировать дома коммутатор это как играться с радиоактивным цезием дома. Можно оборудовать свою хату под эту задачу, но только нахуя, если цель заняться хобби. Вот сделать SDR-радио на FPGA это уже интереснее и реалистичнее, только нихуя статей об этом нет.

А нахуя для этого FPGA? Основа любого цифрового радио - это OCHE BYSTRY ADC, прикрутить к нему какой-нибудь мк с USB 3.0 (или даже USB2.0, если скорости хватит) и всё остальное делать на пекарне.

Будут и коммутаторы. Всему своё время.

А кто говорил о хобби?

Если хочется хобби, то эмуляция ретрокомпов и приставок.

Уважаемый.. Почему счет еще не выставили?

Кое-как выбил такой невъебенный бюджет в пару баксов из тупых невменяемых безмозглых блядей в бухгалтерии которые трахают мозги за каждую ебучую копейку, а ты.. подводишь.

>Что делает? Зачем плис?

>MAX7128S в PLCC84 - клей для всего этого и декодер адресов.

>Ещё тут по сусекам поскрёб, кой чего интересного нашёл. Позже покажу.

ПокажЫ! Вот тебе реально впадлу найти пару микросхем для запуска классики жанра под названием 580ВМ80А?

Запустить не проблема. О - Отлад.ОЧКА этой системы как будет делаться? На этот моменте завис. Мне видится как отдельный мк который может переводить систему в сброс/захват шин, писать-читать ОЗУ, ПЗУ в системе нинужон как ебаная сова.. Перечитай несколько раз и не вздумай ебашить одну FPGA без CPLD рядом для отладки. Для отладки. В живой системе - можно, в отладочной - нет.

Лол. Тоже так соснул когда пробовал писать часы в попытке вывести секунды. Ебнул еще триггер - заработало.

>Всему своё время.

Ага. Время нелепой хуйне — всегда "сейчас". Время хорошим вещам — всегда "скоро". И с ходом времени, что характерно, это не меняется.

>Мне видится как отдельный мк который может переводить систему в сброс/захват шин, писать-читать ОЗУ,

>ПЗУ в системе нинужон как ебаная сова..

Не обязателен микроконтроллер для такого. Один раз пишешь бутлоадер в ПЗУ и далее им пользуешься без навешивания лишнего. Да, конечно адреса немного меняются, но это мелочи.

>какой-нибудь мк с USB 3.0 (или даже USB2.0,

Это cypress infineon fx2lp и fx3, наверное единственный вариант для такого. Или ты знаешь другие микроконтроллеры которые нормально подходят для такого? Только когда начнёшь реально что-то на них делать, то поймёшь что очень многое так просто к ним напрямую не подключить, нужно хотя бы мелкую плисину.

Это даже если ты уверен что нет задачи сделать автономный приемник и твой комп потянет все необходимое (если задача несколько больше чем послушать ментов или дедов).

/ra/даны, а что применяют в дешёвых и не только гигабитных коммутаторах/свичах? Какие-то ASIC'и или ПЛИСины?

Gotcha! Это один из жестких моих просчетов на первой версии.

Про Sprinter и подобные не надо.. Там Z80 со своими особенностями.

Когда нихуя не знаешь и облучение идет методом тыка - переконфигурация ПЛИС начисто валит всю систему когда процессор охуеет от непойми чего на входе из-за наводок Ставь pullup-pulldown? хуй там. Ну задашь NOPы - счетчик команд улетит в бесконечность, когда FPGA прогрущится - хер пойми с какого адреса будет читаться команда/данные.. С жалким подобием контроллЕра на CPLD - можно повесить триггер на захват шин или дернуть вейт - переконфигурить фпга и продолжить выполнение программы далее.

По поводу бутлоадера - не катит. На огрызках найденных плат весь код начинается с 0 адреса и у одной потом идет ремап на 0xF000. Как полезная побочка - внешний МК никак не дает о себе знать основной системе и не занимает никаких ресурсов (типа того же ПЗУ) и например компорта (это каждый раз дрочить-перетыкать кабель если в реальной программе используется компорт и он дк для общения с бутлоадером? ну нахер как и допаивать еще одну вв51а+ви53.)

>Или ты знаешь другие микроконтроллеры которые нормально подходят для такого?

Органическими мозгами поделишься как всю эту парашу погроммировать особенно под винду (и драйвера под все это) для проституток?

Выбирай: FX3, FT601Q от FTDI, CH569W от WCH.

Фотки нет - платка с Али с аррия5 и 2 портами 10G + сетевая карточка в комп и DAC кабели. 2 шланга и считай 20 гигабит можно гнать.

PCI-Express (тред ниже) - тестовая утилитка на говнокомпе на аррия5 показывала около 1.2/1.8 гига в секунду что ли. Чет некогда им заниматься.

Ты какой-то странный.

>На огрызках найденных плат

При чем тут это? Обсуждали вроде как не огрызки.

>мозгами поделишься

Ты накупил говна и не знаешь что с ним делать?

>FT601Q

Не стоит это трогать, оно так себе.

>CH569W

Этот, судя по описанию, уже многое может. Не знал.

>>На огрызках найденных плат

>При чем тут это? Обсуждали вроде как не огрызки.

Ответь про компорт... Когда он один в системе и надо подключить матричный принтер, что-то по модбасу или еще что работающее по компорту. Как в таком случае через бутлоадер отлаживаться, а не тупо залил код и все? При чем без допайки дополнительного компорта.

>Ты накупил говна и не знаешь что с ним делать?

Выдает эффективного менеджера. Про тесты ни разу не слышал или работаем по принципу хуя-хуяк и в продакшен? Особенно когда на тестах всплывают неописанные в даташитах/еррате косяки, несовместимость/отсутствие драйверов/подписей и подобное что нельзя учесть, а в ответ тебе - сам выбирал и жри это говно лишая выбора наиболее подходящего под конкретные условия решения?

А так да. Лежат, жрать не просят. Если интересный проект будет или руководство для проституток - можно попробовать на вкус и посравнивать. Меня останавливает именно говнокодинг под винду и драйвера когда надо пройти кучу кругов ада, ебаные кольца защиты и прочую залупу что бы просто взять и записать-прочитать ебаный байт через PCI шину по адресу устройства которое ему выдалось.. Банальное и простое действие которое хер сделаешь без огроменной анальной боли на пустом месте.

>>FT601Q

>Не стоит это трогать, оно так себе.

Что с ним не так?

Чем лучше/хуже те же 2232H и 4232H? У них есть синхронное фифо и можно мегабайт 30 выжать. в свете эмулятора у них интересен режим эмуляции мастера 8051.

>>CH569W

>Этот, судя по описанию, уже многое может. Не знал.

Осторожно.. Говнецом попахивает. Даташита НЕТ! Есть огрызок где практически ничего не написано. Например покажи описание двух ДМА контроллеров внутри или сердес - только отсылка в лучшем случае - смотрите примеры на гитхабе.

Можно попробовать отсюда начать если будет что-то полезное:

https://hydrabus.com/hydrausb3-v1-0-specifications

Ты странный, высрал кучу малосвязного текста невпопад.

> ASIC'и или ПЛИСины

Оно.

>Время хорошим вещам — всегда "скоро"

Потому-что хорошие вещи быстро не делаются.

>И с ходом времени, что характерно, это не меняется.

Ну в рамках импортозамещения много что появилось, даже перечислять не буду, сам найдёшь если захочешь.

Скажу что уже сейчас есть 100Мб коммутаторы с 1Гб оптикой для связи между собой. И это то что лично видел, может есть ещё что-то.

Также на hh видел вакансию на плисовода в контору которая как раз занимается высокоскоростными коммутаторами, сейчас вакансия уже закрыта, видимо нашли.

>Ну в рамках импортозамещения много что появилось

"Импортозамещено 99% компонентов" где 99% — это всякая обвязка и рассыпуха, а 1% — центральный чип, который не будет повторён никогда. Зато можно отчитаться с красивыми цифрами, создающими впечатление, что вот-вот всё импортозаместим на 100%, если не вдаваться в подробности

>вакансию на плисовода в контору которая как раз занимается высокоскоростными коммутаторами

На виртексах, которые удалось скрысить у пиндосов (по "параллельному импорту").

Почему здесь возникает эта ошибка? Как ее убрать? Пример из книги Панчула "Цифровой синтез".

Error (12014): Net "ledr[1]", which fans out to "ledr[1]", cannot be assigned more than one value

Error (12015): Net is fed by "GND"

Error (12015): Net is fed by "sr_latch:sr_latch|p"

Error (12014): Net "ledr[1]", which fans out to "ledr[1]", cannot be assigned more than one value

Error (12015): Net is fed by "GND"

Error (12015): Net is fed by "sr_latch:sr_latch|p"

А, в книге не так немного, лол.

>cannot be assigned more than one value

Оно тебе пишет человеческим языком, только не русским.

А именно ты более одного раза присваиваешь. Пятую строку убери.

А что означает вот этот синтаксис с точкой .s(key[0]) и в чем его отличие от s(key[0])?

Где взять лицензию/кряк для gowin eda?

Хочу tang nano 9 k пощупать.

Хочу tang nano 9 k пощупать.

>что означает вот этот синтаксис с точкой .s(key[0])

Подключение проводов к твоему модулю по имени.

s - название входа модуля,

key - имя провода который подключается к входу s.

>чем его отличие от s(key[0])

Тем что так компилятор выдаст ошибку.

> Хочу tang nano 9 k пощупать.

Она educatioinal version поддерживается.

Мне пришла Tang Nano 9k. Где у нее клок и как в Gowin IDE вызвать Pin Planner как в квартусе, чтобы задать соответствие между портами и пинами?

Манагер, ты где??? Когда заявку обработаешь?

Проект горит! СРОЧНА НАДА! Еще неделю назад!

Дай счет на оплату!

то есть "AMD или Intel?"

посоны, хочу вкатиться в ПЛИС, на раёне можно урвать примерно за одинаковую цену дев плату со Spartan 6 или со Stratix IV

стратикс новее, в несколько раз мощнее спартана, и круче в плане поддержки периферии, но меня намного больше волнует наличие софта под Linux и отсутствие всяких анальных огороженностей.

что из этих двух ПЛИСов удобнее в этом плане?

посоны, хочу вкатиться в ПЛИС, на раёне можно урвать примерно за одинаковую цену дев плату со Spartan 6 или со Stratix IV

стратикс новее, в несколько раз мощнее спартана, и круче в плане поддержки периферии, но меня намного больше волнует наличие софта под Linux и отсутствие всяких анальных огороженностей.

что из этих двух ПЛИСов удобнее в этом плане?

если это важно, модели плат - Xilinx Spartan 6 SP605 и Altera Stratix IV EP4SGX230

нужна именно PCI-express плата, юсб затычку не хочу

заебал этот квартус. поставил 21.1 квартус прайм, попытался запустить симулятор --- хуй, ошибка была типа nativelink missgin ", оказалось надо было пофиксить строчку в скрипте для nativelink. потом questa стала требовать лицензию, зашёл на сайт получения файла лицензии, попросили зарегаться. заполнил поля, нажал "подтвердить почту", выдало ошибку "Password does not match pattern", нахуй удалил из поля ввода паттерн, прислали код на почту, ввёл, выдало "Password does not match pattern". достал регексп с формы ввода, сгенерил по нему пароль, вставил, рега прошла. пиздец просто.

В каких документах для Tang Nano 9k надо смотреть, к каким пинам чипа привязан клок, светодиоды и кнопки?

Как этим пользоваться? Где посмотреть, например, на каком пине клок, а где кнопки s1 и s2?

> Как этим пользоваться?

Открываешь и читаешь, блять.

Эта ссыль, наверно, более лучще подойдет https://dl.sipeed.com/shareURL/TANG/Nano%209K/2_Schematic

Пасаны, а как в целом китайцы по сравнению с синими и красными? Софт норм, багов много, стоит перекатываться если есть выбор?

>всякая обвязка и рассыпуха

По-твоему не нужна?

>центральный чип

Есть и чипы и процессоры и микроконтроллеры. Производства своего пока нет, но опять таки, это временно.

>На виртексах, которые удалось скрысить у пиндосов (по "параллельному импорту")

Пока да. Пока своих плисин нет можно софт отрабатывать, а там глядишь и элементная база подтянется.

>Есть и чипы и процессоры и микроконтроллеры. Производства своего пока нет

Лол.

>но опять таки, это временно

Тебе сколько лет, пять? Мне давно уже не пять лет, увы.

>Лол.

Хуёл.

>Мне давно уже не пять лет

А ума так и нет.

отвечу сам себе: поддержка Stratix IV есть только в платной версии софта Intel® Quartus® Prime Standard Edition Software

а есть опенсорц или хотя бы бесплатное IDE с поддержкой Stratix IV?

> а есть опенсорц или хотя бы бесплатное IDE с поддержкой Stratix IV?

С какого перепугу?

кароч если очень хочется интел, то нужно искать дев кит с одним из этих чипов

да хз, я чото думал, что c FPGA так же, как с ардуиной - скачал бесплатное иде, хуяк-хуяк и мигаешь лампочками, а тут пиздецы какие-то с downloads по 25 гигабайт и анальными регистрациями.

с Xilinx всё так же плохо?

> да хз, я чото думал, что c FPGA так же, как с ардуиной

Здеся вам не тута. Там всё анально огорожено, единственное исключение: https://github.com/YosysHQ/nextpnr

> с Xilinx всё так же плохо?

Там ещё хуже: https://docs.xilinx.com/r/en-US/ug973-vivado-release-notes-install-license/Supported-Devices

Плюс

> Xilinx Unified Installer 2022.2 SFD (TAR/GZIP - 89.4 GB)

в интернетах вроде пишут, что Lattice - нарм FPGA без анального рабства ну разве что самую малость, это правда?

чем они лучше/хуже по сравнению с Xilinx/Altera?

чем они лучше/хуже по сравнению с Xilinx/Altera?

Ты идиот? На рутрекере забанен?

🤔 я так давно пользуюсь линуксом, что уже забыл про существование торрентов, лол

И не то что в игрушки не играешь, так ещё даже кинцо спираченное смотришь?

С опенсурсными сапрами все очень плохо, нечего тут удивляться. Даже чертить как следует не в чем. Фрикад это максимум, для любителей как я оно сойдёт, но оно же безнадежно сольет компасу например. И с остальными сапрами аналогично.

>кинцо

Почти никогда не стоит потраченного времени.

>игрушки

У Габена тупо удобнее. Не просто исталл в один клик, но и весь пердолинг с wine/proton выполняется автоматически без вмешательства пользователя.

> кинцо

не смотрю

> игрушки

почти не играю что пару часов перед сном поаутировать в майнкрафт не считается

погуглив ещё немного, я узнал, что огромное количество логических элементов не нужно - для реализации софтового процессора типа https://github.com/f32c/f32c достаточно и спартана 6 или циклона 4.

гуглю дальше.

думаю, остановлюсь на циклоне 4 или 5.

бамп вопросу

Уважаемый менеджер, Вы куда пропали?

Заказ горит, а Вы еще счет на оплату и согласование не выставили. Что мне говорить за проеб сроков из-за Вашей нерасторопности?

СРОЧНО НУЖЕН СЧЕТ НА СОГЛАСОВАНИЕ!!!! СРОЧНА!!!

Анон с профессорами репортинг.

>Вот тебе реально впадлу найти пару микросхем для запуска классики жанра под названием 580ВМ80А?

Моет быть, когда-нибудь, но это не точно. Дел и без этого хватает.

>ПокажЫ!

Немного разобрал своё барахлишко, осталась мелкая рассыпуха и импортная база.

В общем вот чем располагаю на данный момент.

>Уважаемый менеджер, примите заказ:

>CYRS1645KV18-250GCMB 144-Mbit QDR® II+ SRAM - нужно 20 шт

>MT29F128G08AMCABH2-10ITZ:A (Micron NAND Flash SLC 128G 16GX8) - 32 шт

И где это можно купить?

>8A34041 (8-Channel Universal Frequency Translator)

Для генерации частоты чтоль? Не проще на рассыпухе собрать?

>AD9213 (radio frequency (RF) analog-to-digital converter (ADC)) - 13 шт

>ZU48DR-G1517 (Xilinx ZYNQ UltraScale+ RFSoC) - 10 шт

Это ещё зачем?

>Вот тебе реально впадлу найти пару микросхем для запуска классики жанра под названием 580ВМ80А?

Моет быть, когда-нибудь, но это не точно. Дел и без этого хватает.

>ПокажЫ!

Немного разобрал своё барахлишко, осталась мелкая рассыпуха и импортная база.

В общем вот чем располагаю на данный момент.

>Уважаемый менеджер, примите заказ:

>CYRS1645KV18-250GCMB 144-Mbit QDR® II+ SRAM - нужно 20 шт

>MT29F128G08AMCABH2-10ITZ:A (Micron NAND Flash SLC 128G 16GX8) - 32 шт

И где это можно купить?

>8A34041 (8-Channel Universal Frequency Translator)

Для генерации частоты чтоль? Не проще на рассыпухе собрать?

>AD9213 (radio frequency (RF) analog-to-digital converter (ADC)) - 13 шт

>ZU48DR-G1517 (Xilinx ZYNQ UltraScale+ RFSoC) - 10 шт

Это ещё зачем?

Да вы батенька мажор... Есть же игрушки из 580 серии.

Например 580ВИ53 - таймер и рядом 580ВВ51А - компорт можно собрать (и написать бутлоадер как завещал анон )

589ИР12 - порт ввода ИЛИ вывода (только одно направление навсегда) или его в мусор (ладно, к 580ВТ57 приделаешь и получишь 4х анальный ДМА) и взять 580ВВ55А - получишь целых 3 порта по 8 бит.

537РУ10 - внезапно ОЗУ на целых 2 килообайта!

Если любишь аборты и прерывания - 1810ВН59А.

Во всякие хххРЕхх (программируемые ПЗУ) не вникал - вряд ли есть чем их погроммировать и могут быть нестандартные напряжения питания. Остальные микросхемки тоже позже посмотрю - вдруг что вкусное есть.

Системного контроллера не увидел как и генератора.

Не собирал, один из вариантов замены на рассыпчатой логике здесь -> http://rw6hrm.qrz.ru/8080.htm

По поводу поста

> И где это можно купить?

Ты же менеджер по продажам, сам должен найти где купить и главное - менее чем 8 центов за чип да еще и с учетом доставки!!!

>>8A34041 (8-Channel Universal Frequency Translator)

>Для генерации частоты чтоль? Не проще на рассыпухе собрать?

Почитал бы что за ядреная херня. Вряд ли на рассыпухе такое соберешь если это вообще возможно.

>>AD9213 (radio frequency (RF) analog-to-digital converter (ADC)) - 13 шт

>>ZU48DR-G1517 (Xilinx ZYNQ UltraScale+ RFSoC) - 10 шт

>Это ещё зачем?

BMS на литиевую батарейку делать. Процессы там медленные и нужны медленные АЦП что бы записывать и смотреть как идет заряд-разряд батареи. Судя по параметрам этих АЦП их с огромным скрипом и натягом должно хватить на жалкое подобие детекторного приемника с околонулевой селективностью.

И вообще - какая разница менеджеру куда и зачем такие детальки? Его задача найти где купить, накрутить цену и продать. Когда счет выставишь то? Долго еще ждать? Начальство уже все злое ходит из-за срыва сроков поставок..

О

А что за клоны хилых есть у китайцев и сколько они стоят?

С pango еще никто не работал?

С pango еще никто не работал?

> А что за клоны хилых есть у китайцев

Вам не дадут. Это для солидных людей с юридическим еблом, а не для гаражных ниггеров: https://electronix.ru/forum/index.php?controller=topic&id=165881

да, они не очень огорожены - раздают бесплатные лицензии для iCE40

https://www.latticesemi.com/Products/DesignSoftwareAndIP/FPGAandLDS/Radiant

если есть какие-то неочевидные нюансы - напишите, пожалуйста.

У меня есть плата cmod A7 35T. Нашел schematic к ней, а там у диодов не подписаны пины, к которым они соединены. Может я слепой, где тут указаны пины для кнопок и диодов?

https://digilent.com/reference/_media/reference/programmable-logic/cmod-a7/cmod_a7_sch.pdf

https://digilent.com/reference/_media/reference/programmable-logic/cmod-a7/cmod_a7_sch.pdf

Смотри лучше. 3 страница нижний левый угол. Читаем название выводов и идем на правую часть 1й страницы. Сопоставляем.

Как в FPGA реализуется получение, хранение, коммутирование и выдача данных, например, при решении уравнений?

На мутный и общий вопрос мутный и общий ответ в Альтеровской нотации.

> получение

> выдача данных

Через блоки вводы-вывода. Можно параллельно или последовательно в виде униполярных или дифференциальных сигналов, можно через блоки SERDES (только в последовательном виде).

>хранение

На триггерах и/или в блоках памяти (MLAB, EAB, M4K, M9K, M144K.. которые работают как двухпортовая память или как FIFO). Можно хранить и в триггерах блоков ввода-вывода - например при реализации DDR памяти и оттуда читать-писать.

> коммутирование

Внутренние матрицы межсоединений/коммутации. Надо смотреть описание LAB и как они между собой соединяются - это если на уровне кристалла и напрямую недоступно. На уровне описания аппаратуры в большинстве случаев - мультиплексор. Самый обычный мультиплексор (да и то не всегда нужен если например выход регистра результата сразу выдавать на внешние контакты)

https://marsohod.org/11-blog/265-fpga

Я имел в виду, как все это делается на той стороне, с которой работает инженер. Как инженер загружает данные в ПЛИС, как эти данные там хранятся, как они выгружаются обратно. Типа как база данных и бизнес-логика для обработки данных на бэкэнде джава.

Ну вот например, можно загрузить данные для обработки по uart или как-то еще? Хранить их в регистрах, массивах или писать какой-то буффер типа очереди или стека? Вот это меня интересует

Берёшь ip ядро уарта, или делаешь свой. Пользуешься.

У тебя странные рассуждения. Там ведь по сути схема создаётся, пусть из одинаковых ячеек. И рассуждать нужно применительно к схеме, а не языку программирования. Это если про синтезируемый код конечно.

>массивах

Для начала ответь на вопрос о том как это будет выглядеть внутри плисину, что будет задействовано и в каком количестве. И про остальные буферы то же самое. Как начнёшь понимать вот это, то и твой вопрос сам отпадет.

> можно загрузить данные для обработки по uart или как-то еще?

Можно и по uart. Из распространённых протоколов есть ещё Ethernet и по желанию стек tcp/ip.

>Хранить их в регистрах, массивах или писать какой-то буффер типа очереди или стека?

Можно и в регистрах, если массив небольшой. А можно и в ОЗУ - если большой. Очередь или стек, если опять таки большие, делаются на базе ОЗУ, а что именно из этого это уже по ситуации, что удобнее.

Есть один кинтекс7, точнее не есть, а будет через пару недель. Но к тому моменту нужен минимально рабочий проект. В проекте понадобятся встроенные dsp. Я с ними ни разу не работал, да и вообще в плисах опыт совсем чуть больше нуля и только со спартанами6. Так что реквестирую способы симуляции для него.

Могу ли я поставить принудительно лицензированную виваду и посмотреть там RTL того, что понапишу на верилоге? Увижу ли я в этой RTL, что dsp48e1 используется? Есть ли у неё встроенный симулятор как у ISE, и что он симулирует, только поведение модуля, описанного верилогом, или прям полностью то что есть в ПЛИС?

Могу ли я поставить принудительно лицензированную виваду и посмотреть там RTL того, что понапишу на верилоге? Увижу ли я в этой RTL, что dsp48e1 используется? Есть ли у неё встроенный симулятор как у ISE, и что он симулирует, только поведение модуля, описанного верилогом, или прям полностью то что есть в ПЛИС?

>реквестирую способы симуляции для него

В коде пишешь m <= a * b; и симулируешь. В редакторе схем смотришь, что оно синтезируется в DSP48.

>Могу ли я поставить принудительно лицензированную виваду и посмотреть там RTL того, что понапишу на верилоге? Увижу ли я в этой RTL, что dsp48e1 используется? Есть ли у неё встроенный симулятор как у ISE, и что он симулирует, только поведение модуля, описанного верилогом, или прям полностью то что есть в ПЛИС?

Да, да, да, да, ни то ни другое, а собственную модель, которая по задумке должна совпадать и с поведением кода, и с поведением блока в плис. Если то, что ты написал, невозможно синтезировать в DSP48 (например, требует больше бит, чем есть), синтезатор не будет пытаться изменить поведение кода, чтобы впихнуть его в DSP48, а просто сделает простыню из LUTов. В таком случае надо открывать даташит/гайдлайны и искать, какие части переписать.

О, класс. Спасибо!

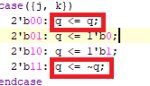

Почему в тестбенче в переменной q всегда значение 'x'? Оно должно меняться при изменении состояния триггера.

Потому что у тебя описан триггер с динамическим управлением, т.е. оно должно срабатывать при изменении clk с 0 на 1. А такое изменение у тебя в тестбенче только в одном месте - 11 и 12 строки, но там у тебя j=k=1, а значит оно должно проинвертировать свое состояние там. Только начальное значение у тебя неопределенно, т.е. 1'bx, соответственно инверсия также даёт 2'bx. Измени тестбенч, можешь ещё задать начальное состояние триггера.

Также jk триггеров со статическим управлением (то есть как предусматривает твой тестбенч) не бывает толком, потому что при j=k=1 оно превратиться в генератор. Конечно есть варианты, но пока не стоит рассматривать их.

>также даёт 2'bx

1'bx, по кнопке промазал.

Это вот так делается, чтобы был переход clk с 0 на 1? Все равно в q находится x.

Задержку добавь после clk=0 везде.

почему пишет

Error (10734): Verilog HDL error at qqq.v(17): i is not a constant

module cgncgh(output reg [31:0]REG, input [1:0]L, input [7:0]D, input C);

reg [7:0]REGA[3:0];

always @(posedge C)

case(L)

2'd0: REGA[0] <= D;

2'd1: REGA[1] <= D;

2'd2: REGA[2] <= D;

2'd3: REGA[3] <= D;

endcase

always @(ж)

begin

integer i;

for(i=0; i<=3; i=i+1)

REG[8i+7:8i] = REGA[7:0];

end

endmodule

Error (10734): Verilog HDL error at qqq.v(17): i is not a constant

module cgncgh(output reg [31:0]REG, input [1:0]L, input [7:0]D, input C);

reg [7:0]REGA[3:0];

always @(posedge C)

case(L)

2'd0: REGA[0] <= D;

2'd1: REGA[1] <= D;

2'd2: REGA[2] <= D;

2'd3: REGA[3] <= D;

endcase

always @(ж)

begin

integer i;

for(i=0; i<=3; i=i+1)

REG[8i+7:8i] = REGA[7:0];

end

endmodule

>REG[8i+7:8i] = REGA[7:0];

REG[8✶i+7:8✶i] = REGA[7:0];

Можно было бы подумать, что с массивами так не работает, но нет, такой код вполне компилится:

И в чём между ними принципиальная разница?

module cgncgh(output reg [31:0]REG, input [1:0]L, input [7:0]D, input C);

reg [7:0]REGA[3:0];

reg [7:0]REGB[3:0];

always @(posedge C)

begin

case(L)

2'd0: REGA[0] <= D;

2'd1: REGA[1] <= D;

2'd2: REGA[2] <= D;

2'd3: REGA[3] <= D;

endcase

end

always @(✶)

begin

integer i, j;

for(j=0; j<=3; j=j+1)

for(i=0; i<=7; i=i+1)

REGB[j] = REGA[j][7-i];

end

always @(✶) REG = {REGB[3], REGB[2], REGB[1], REGB[0]};

endmodule

Верилог не может выбирать подмассивы с границами, которые заданы переменными. Даже если код написан так, что ширина подмассива всегда постоянна.

Понять и простить.

То, что ты хочешь, можно сделать при помощи genvar/generate — это тоже переменная, но все её значения обсчитываются только при синтезе схемы, и для каждого варианта генерируется собственный блок.

genvar group_idx;

generate

for (group_idx=0; group_idx<4; group_idx=group_idx+1) begin : connecting_subarray_groups

always @(×) EG[8×group_idx +: 8] = REGA[0 +: 8];

end

endgenerate

>Верилог не может выбирать подмассивы с границами, которые заданы переменными. Даже если код написан так, что ширина подмассива всегда постоянна.

Всё равно не понял.

Здесь

>REG[8✶i+7:8✶i] = REGA[7:0];

и здесь

>REGB[j] = REGA[j][7-i];

используется переменная в индексе массивов, но один код компилится, другой почему-то нет.

Тут не происходит выбора подмассива с некоторой вычисляемой (и поэтому формально неизвестной) шириной. Либо выбор элемента из массива, либо выбор одного бита.

И КСТАТИ НЕ ОРИ КОГДА ДАЁШЬ НАЗВАНИЯ ЦЕПЯМ И РЕГИСТРАМ, ЭТО СМОТРИТСЯ СТРАННО. ОРУТ ОБЫЧНО КОГДА НАЗЫВАЮТ ПАРАМЕТРЫ МОДУЛЯ

>Тут не происходит выбора подмассива с некоторой вычисляемой (и поэтому формально неизвестной) шириной. Либо выбор элемента из массива, либо выбор одного бита.

Как-то ты витиевато пишешь.

В общем я разобрался, вот так работает

for(i=0; i<=31; i=i+1)

REG = REGA[i/8][i%8];

Недопустимы переменные в левой части присвоения.

Во-первых, не работает. У тебя всё присваивается в младший бит.

Во-вторых, это какой-то пиздец и клоунада, а не код. Попробуй так штоле:

for(i=0; i<4; i=i+1)

for(j=0; j<8; j=j+1)

REG[i*8+j] = REGA[j];

Очепятался мальца

>REG = REGA[i/8][i%8];

REG = REGA[i/8][i%8];

И оговорился в добавок

>Недопустимы переменные в левой части присвоения.

Недопустимы вычисления в левой части присвоения.

У тебя как раз вычисления

>REG[i*8+j] = REGA[j];

так не сработает.

сука, мамка разметку жрёт

REG[ i ] = REGA[i/8][i%8];

>так не сработает.

Чел, ты попробуй.

> мамка

ты ещё и с мобилы капчуешь?

>мамка разметку жрёт

Ага, по ней это сразу видно)))

Вообще пиздец.

Попробовал

Warning (10230): Verilog HDL assignment warning at cgncgh.v(22): truncated value with size 8 to match size of target (1)

Error (10251): Verilog HDL error at cgncgh.v(22): index 4 cannot fall outside the declared range [3:0] for dimension 0 of array "REGA"

Так, секунду. Мамка сожрала разметку)))

for(i=0; i<4; i=i+1)

for(j=0; j<8; j=j+1)

REG[i*8+j] = REGA[i][j];

Почему этот счетчик не считает и модуль не мигает диодом?

Та же проблема, что

А, ты хочешь сказать что НЕдопустимы вычисления в диапазонах?

Т.е. REGA[xy] допустимо, а REGA[xy:x*y+1] уже нет?

Ну хорошо, а чем тебе мой вариант не угодил?

>Т.е. REGA[xy] допустимо, а REGA[xy:x*y+1] уже нет?

Оу уж эта мамка

Т.е. REGA[x✶y] допустимо, а REGA[x✶y:x✶y+1] уже нет?

Или даже может так

REGA[x:x+1] - недопустимо?

Ну вот, ты понял. А всего-то надо было чуть-чуть вчитаться, если сходу не дошло.

>Ну хорошо, а чем тебе мой вариант не угодил?

Тем, что это нечитаемо и неподдерживаемо. Если через месяц тебе надо будет что-нибудь там подправить, то вспомнить, что ты имел в виду, потребует больше времени, чем нужно было, чтобы это придумать и написать.

Есть ещё варик, когда вычисляется одна граница, а ширина явно даётся константой: REG[8*j +: 8] = REGA[j];

В икарусе это поддерживается. Тут надо иметь в виду, что в разных инструментах одна и та же конструкция может поддерживаться, а может и нет.

В икарусе это поддерживается. Тут надо иметь в виду, что в разных инструментах одна и та же конструкция может поддерживаться, а может и нет.

Хорошая плата? Хочу себе плату с переключателями, индикаторами и периферией.

https://aliexpress.ru/item/1005003530412307.html?sku_id=12000029522416357&spm=a2g2w.productlist.search_results.10.5b324aa6LGogUI

https://aliexpress.ru/item/1005003530412307.html?sku_id=12000029522416357&spm=a2g2w.productlist.search_results.10.5b324aa6LGogUI

Ищи с циклоном 4, первый циклон совсем уж днище. А периферия тут обычная, за такие деньги богаче не найдёшь.

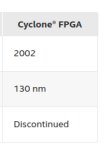

> EP1C3T144

Как там у вас, в 2003?

> Хочу себе плату с переключателями, индикаторами и периферией.

Накинь тысчёнку другую и«Get a real computer!»:

https://aliexpress.ru/item/4000837637863.html

https://aliexpress.ru/item/1005004653308809.html

Ну или возьми Tang Nano 9K, вдвое дешевле и для хлебницы :

https://www.aliexpress.ru/item/1005003803994525.html

>Tang Nano 9K

Уж лучше древний квартус из 2003, чем говеновское еда.

Кстати, Gowin умеет в Ethernet MAC?

Какой DDR можно к нему подцепить?

Какой DDR можно к нему подцепить?

>https://aliexpress.ru/item/4000837637863.html

Для этой штуки схема есть? Посмотреть, куда подключаются семисегментные индикаторы.

> Для этой штуки схема есть?

А хуйЪ его знает. На их сайте только для варианта с шестым спартаном: http://piswords.com/pix16.html

P.S. На вот эту плату https://aliexpress.ru/item/1005002986003759.html точно есть: https://github.com/jvitkauskas/Altera-Cyclone-IV-board-V3.0

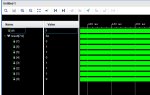

Почему схема не работает? Сигнал clk подсоединен к кнопке, сигналы lfsr[0]-lfsr[7] соединены с диодами. Диоды должны загораться случайно при нажатии на кнопку, а они горят все одновременно. Плата C4E6/E10-CORE

А в ввиваде lfsr8 нормально симулируется, случайные числа генерируются.

Открой implemented design→schematic и проверь, что схема соответствует ожидаемому.

Вроде соответствует. Три xor гейта и регистр сдвига (7 триггеров)

1. Не факт что присвоение в шапке модуля синтезируемо.

2. Куда у тебя подключена кнопка, к clk чтоль?

Ресет возник из ниоткуда, куда он выведен? Он наводки не ловит? Попробуй пару диодов отсоединить от регистра и подключить к clk и reset, чтобы смотреть, что на них происходит.

>Куда у тебя подключена кнопка, к clk чтоль?

Да, тактирую руками

>Ресет возник из ниоткуда, куда он выведен?

Дописал потом. Выведен на вторую кнопку.

1. Убедись что кнопка в отжатом состоянии даёт 0, очень может быть что наоборот.

2. По ресету у тебя регистр обнуляется, после этого работать уже не будет, при нулях сумма по модулю даёт 0.

3. Попробуй присвоение в шапке убрать и заменить на

initial lfsr <= 8'd255;

4. Кнопка даёт дребезг, но сейчас это значение не имеет.

>initial lfsr <= 8'd255;

Спасибо, помогло.

>Убедись что кнопка

Кнопка ресета.

Задам пару нубских вопросов.

1) ПЛИС можно программировать, вроде, без написания кода собирая цифровое устройство визуально - соединяя отдельные логические элементы между собой? Потом они "прожигаются" уже в самой ПЛИС и по итогу получается нечто похожее на изготовленню на заводе микросхему? В смысле получается устройство как обычные микросхемы двоичной логики - счетчики всякие, дешифраторы и прочее.

2) Так как ПЛИС это не микропроцессор то стабильность работы у нее будет выше? Ведь вероятность глюка в жесткой логике куда ниже - нечему зависнуть в отличие от целого микроконтроллера с постоянной и оперативной памятью, АЛУ с его вычислениями и прочим. Это похоже на зависания контроллеров китайских для елочных гирлянд и дубовой стабильной работе простых мигалок для тех же гирялнд по схемах из нескольких деталей.

1) ПЛИС можно программировать, вроде, без написания кода собирая цифровое устройство визуально - соединяя отдельные логические элементы между собой? Потом они "прожигаются" уже в самой ПЛИС и по итогу получается нечто похожее на изготовленню на заводе микросхему? В смысле получается устройство как обычные микросхемы двоичной логики - счетчики всякие, дешифраторы и прочее.

2) Так как ПЛИС это не микропроцессор то стабильность работы у нее будет выше? Ведь вероятность глюка в жесткой логике куда ниже - нечему зависнуть в отличие от целого микроконтроллера с постоянной и оперативной памятью, АЛУ с его вычислениями и прочим. Это похоже на зависания контроллеров китайских для елочных гирлянд и дубовой стабильной работе простых мигалок для тех же гирялнд по схемах из нескольких деталей.

>А всего-то надо было чуть-чуть вчитаться, если сходу не дошло.

Просто ты витиевато пишешь, сказал бы сразу

>в диапазонах недопустимо

>неподдерживаемо

Кактус вполне синтезит.

>потребует больше времени

Для этого не скупиться на жирные комментарии.

Слушай, раз такое дело, может ещё подскажешь

Чем отличаются записи

-4'd5 от -4'sd5

Я отличий не заметил.

И ещё, решил полистать стандарт на верилог и не нашёл где указывается разрядность переменных типа integer и time. Я не думаю, что это оставили на усмотрение разработчикам компиляторов, во всех книжках пишут, что integer это 32 разряда.

Есть какие-нибудь возможности программировать FPGA на си или C++? Вроде в виваде есть какой-то HLS. Было бы интересно писать параллельные алгоритмы на высокоуровневом языке.

> ПЛИС можно программировать, вроде, без написания кода собирая цифровое устройство визуально

Да. Только зачем? Что-то стоящее таким образом не соберёшь - устанешь. Для этого придумали автоматизацию, называется HDL, оно же языки проектирования аппаратуры. Грубо говоря, если тебе нужно нарисовать счётчик на 64 разряда, то ты бы все 64 разряда рисовал руками, на HDL достаточно создать один разряд и поставить его в цикл на 64 раза.

>Потом они "прожигаются" уже в самой ПЛИС и по итогу получается нечто похожее на изготовленню на заводе микросхему? В смысле получается устройство как обычные микросхемы двоичной логики - счетчики всякие, дешифраторы и прочее.

До переброса питания. ПЛИС типа FPGA свою прошивку хранит во внешней флешке, и по подаче питания начинает процесс инициализации, переписывает прошивку из флешки себе во внутреннюю энергоЗависимую память.

>Так как ПЛИС это не микропроцессор то стабильность работы у нее будет выше?

Не факт.

В старом железе, где процессор и ОЗУ были связаны между собой шиной проходящей по печатной плате, на эту шину можно было легко навести помеху от чего программа сбоила. Там да, стабильность была низкая.

Микроконтроллеры это тоже схема из

>счетчики всякие, дешифраторы и прочее

вместе с ОЗУ выполненные интегрально и навести туда помеху уже не так просто.

Так что скорее всего на ровне.

Копай в сторону SystemC

О нём давно говорят, но что-то как средство синтеза, как и прочее на эту тему, пока не взлетает.

> Да. Только зачем? Что-то стоящее таким образом не соберёшь - устанешь. Для этого придумали автоматизацию, называется HDL, оно же языки проектирования аппаратуры. Грубо говоря, если тебе нужно нарисовать счётчик на 64 разряда, то ты бы все 64 разряда рисовал руками, на HDL достаточно создать один разряд и поставить его в цикл на 64 раза.

Да не умею я просто в программирование. Вот и подумал что можно было бы что-то не сильно сложное запрограммирвать визуальным соединением блоков.

> До переброса питания. ПЛИС типа FPGA свою прошивку хранит во внешней флешке, и по подаче питания начинает процесс инициализации, переписывает прошивку из флешки себе во внутреннюю энергоЗависимую память.

Хм, вот как.

> Не факт.

> В старом железе, где процессор и ОЗУ были связаны между собой шиной проходящей по печатной плате, на эту шину можно было легко навести помеху от чего программа сбоила. Там да, стабильность была низкая.

> Микроконтроллеры это тоже схема из

> вместе с ОЗУ выполненные интегрально и навести туда помеху уже не так просто.

> Так что скорее всего на ровне.

Спасибо.

>Да не умею я просто в программирование. Вот и подумал что можно было бы что-то не сильно сложное запрограммирвать визуальным соединением блоков.

тогда бери owen logic

Спасибо.

>Да не умею я просто в программирование.

Ну чё, в Квартусе есть графический редактор.

А вообще можешь начать

https://www.youtube.com/@Jack0v/playlists

>Кактус вполне синтезит.